We have two weeks to go on our crowdfunding campaign, which will close on the 24th of October.

The response to the campaign so far has been “not great, not terrible”. We hope to receive more orders in the near future.

Planning for less units than anticipated has a few consequences:

- It reduces complexity during manufacturing. For example, we can manually test the motherboards rather than building a test rig.

- By taking on little additional risk, we can make the units faster, for example by ordering more PCBs. The only component we don’t have in stock is the SN220E, which needs to be programmed with our own keys at the fab (keys we don’t have yet, so not shipping the SN220E seems reasonable for the time being).

- Due to the reduced budget, it is unlikely that we will have units in stock for people to buy off the shelves next year. On the same note, if volumes don’t pick up after the product is verified as working in other people’s hands, we will need to raise prices significantly.

Overall, we remain optimistic that this new paradigm we are introducing in the world of software defined radios is going to take hold, and we are bracing (economically) for the long winter before that materialises.

And with that out of the way, onwards to the technical updates:

Motherboard v2 (almost) ready for manufacturing

During bringup and rework of the first motherboard, we took seven pages worth of notes (2200 words) on things to improve. All but two points are now addressed, and the new PCB is almost ready for being sent to manufacturing.

What’s left to verify:

- The LA9310’s DAC isn’t working, we believe because of a software issue.

- There is an important noise problem at the output of the ADCs (the sampling clock is basically being fed through and only losing ~40dB in the process). This doesn’t show up on the sampled data as it’s a multiple of the sampling clock, but it’s important that we fix this.

- We are porting a different BSP to try and address both issues, but are holding the second batch until we can rule out a bad PCB design.

The visible improvements are few:

- The board can now be powered via USB, even when the source is not capable of negotiating a USB Power Delivery connection, as long as it can supply more than 2A. Input voltages below the rated 5V (because of bad cables, for example) won’t be a problem thanks to the new buck-boost converter. There are a myriad of other improvements to the power supply and USB power sections.

- Optional copper tape shielding for the exposed side of the motherboard: we found that in exceptional circumstances (using the embedded daughterboard antenna to receive GPS), broadband high frequency noise coming from the decupling capacitors can affect the noise floor of the embedded antennas at the daughterboard. We are exposing some copper and protecting the capacitors with conformal coating to allow for a simple DIY fix (for the 1% of users that will end up needing this).

Motherboard heatsink gets an (inaudible) fan

We are increasing the height of the motherboard CNC enclosure significantly to embed a low-profile, ultra-quiet fan into it. You won’t be able to tell it’s there, but it’s going to help with thermals. It’s not required, as the motherboard only has a delta-T of around 35C over ambient at 10W power consumption (with no heatsink on the daughterboard and that heat contributing significantly to the temperature raise, which won’t be the case once we have heatsinks for the daughterboards).

This adds a lot to the total system cost (fan cost, extra milling and material for the CNC enclosure and assembly time), but we want to do it to make the product durable and stable over time.

I/Q imbalance calibration

We now have a LA9310 DSP core that can do 5-tap QEC (Quadrature Error Correction), filtering and down-conversion. QEC is paramount to achieve great (50dB+) rejection between a sampled signal and its image on the negative part of the spectrum. This usually requires an active calibration loop, using the DAC to generate a sweeping sinewave. There are other ways, for example the Granita RFIC has an embedded calibration mode, the Lime RFIC can simply use TX LO leakage, and given a continuous stream, you can simply assume it has to be complex data and run some smart real-time calibration on it.

I/Q QEC limitation on the secondary daughterboard

The secondary daughterboard doesn’t have a DAC path, so it cannot use a sinewave from the LA9310 to run calibration (there are other ways, as explained above).

This is a limitation only as long as you want to sample at 153 MSPS on the secondary daughterboard, as if you are happy with 76 MSPS, the trivial solution is to do real rather than complex sampling (by sampling either I or Q, you get rid of the need to run QEC calibration entirely).

Granita RFIC updates

This is a mixed bag. Some bits are good: for example, Arctic Semi has provided us with sample code that can tune the PLL in less than 2 milliseconds, which will result in a super-inexpensive RTSA with sweep speeds up to 60 GHz per second (using the two PLLs and the frontend switching to sample and tune at the same time).

However, we are still limited in the frequency range we can tune to, which means that the validation of our Granita daughterboard has stalled.

We hope this issue can be addressed soon. If it isn’t, our worst case scenario is scrapping the daughterboard and re-developing with a different 5G RFIC.

Our local components stock

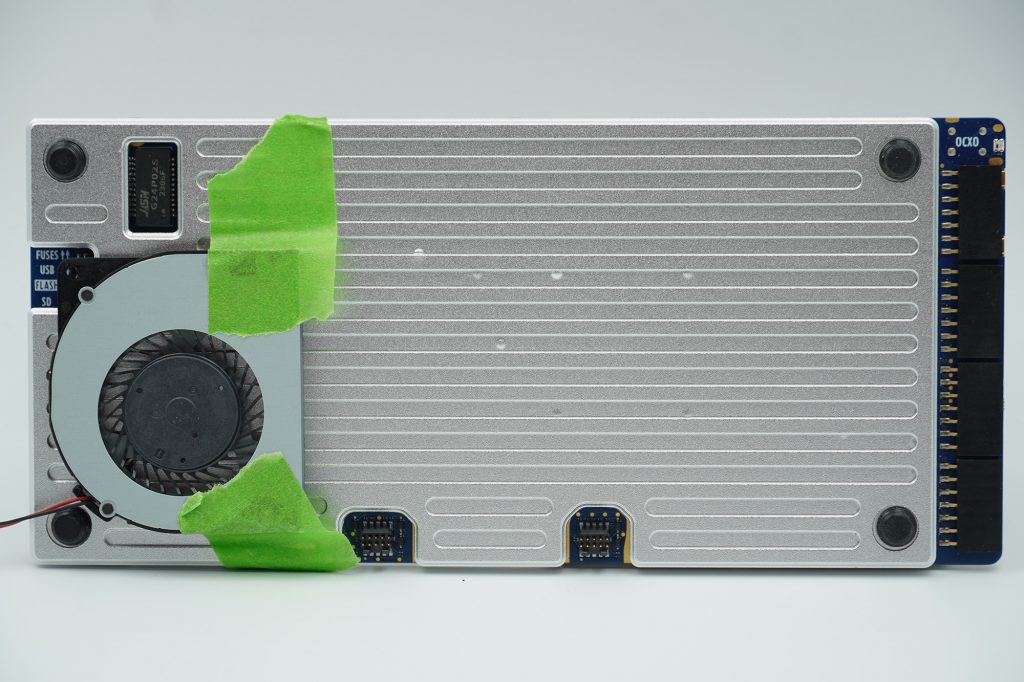

What happens when you spend an entire year collecting parts, hedging against supply chain disruptions? We are leaving you with a self-explanatory picture.